# **BIRSA INSTITUTE OF TECHNOLOGY (TRUST)**

# NH-33, GETLATU, RANCHI

Department: - Electronics and Communication Engineering Lecture notes Semester: - 4<sup>th</sup> Subject: - Digital Technologies and Microprocessor Lecturer: - Alok Kumar Singh

# UNIT -V

# Interrupts in 8086 Microprocessor

# Interrupts

**Definition:** The meaning of 'interrupts' is to break the sequence of operation. While the CPU is executing a program, on 'interrupt' breaks the normal sequence of execution of instructions, diverts its execution to some other program called Interrupt Service Routine (ISR). After executing ISR, the control is transferred back again to the main program. Interrupt processing is an alternative to polling.

**Need for Interrupt**: Interrupts are particularly useful when interfacing I/O devices that provide or require data at relatively low data transfer rate.

**Types of Interrupts:** There are two types of Interrupts in 8086. They are: (i)Hardware Interrupts and

(ii)Software Interrupts

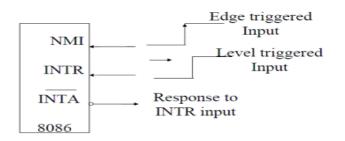

(i) **Hardware Interrupts** (External Interrupts). The Intel microprocessors support hardware interrupts through:

- Two pins that allow interrupt requests, INTR and NMI

- One pin that acknowledges, INTA, the interrupt requested on

INTR. INTR and NMI

- INTR is a maskable hardware interrupt. The interrupt can be enabled/disabled using STI/CLI instructions or using more complicated method of updating the FLAGS register with the help of the POPF instruction.

- When an interrupt occurs, the processor stores FLAGS register into stack, disables further interrupts, fetches from the bus one byte representing interrupt type, and jumps to interrupt processing routine address of which is stored in location 4 \* <interrupt type>. Interrupt processing routine should return with the IRET instruction.

- NMI is a non-maskable interrupt. Interrupt is processed in the same way as the INTR interrupt. Interrupt type of the NMI is 2, i.e. the address of the NMI processing routine is stored in location 0008h. This interrupt has higher priority than the maskable interrupt.

- – Ex: NMI, INTR.

(ii) **Software Interrupts** (Internal Interrupts and Instructions) .Software interrupts can be caused by:

- INT instruction breakpoint interrupt. This is a type 3 interrupt.

- INT <interrupt number> instruction any one interrupt from available 256 interrupts.

- INTO instruction interrupt on overflow

- Single-step interrupt generated if the TF flag is set. This is a type 1 interrupt. When the CPU processes this interrupt it clears TF flag before calling the interrupt processing routine.

- Processor exceptions: Divide Error (Type 0), Unused Opcode (type 6) and Escape opcode (type 7).

- Software interrupt processing is the same as for the hardware interrupts.

- - Ex: INT n (Software Instructions)

- Control is provided through:

- IF and TF flag bits

- IRET and IRETD

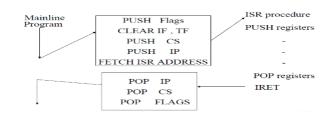

# **Performance of Software Interrupts**

- 1. It decrements SP by 2 and pushes the flag register on the stack.

- 2. Disables INTR by clearing the IF.

- 3. It resets the TF in the flag Register.

- 5. It decrements SP by 2 and pushes CS on the stack.

- 6. It decrements SP by 2 and pushes IP on the stack.

- 6. Fetch the ISR address from the interrupt vector table.

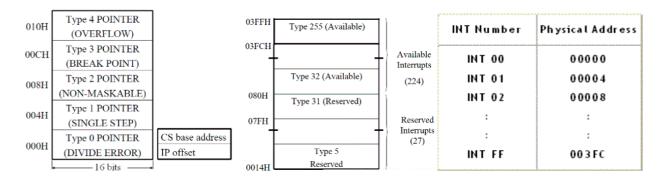

# **Interrupt Vector Table**

#### Functions associated with INT00 to INT04

#### INT 00 (divide error)

- INT00 is invoked by the microprocessor whenever there is an attempt to divide a number by zero.

- ISR is responsible for displaying the message "Divide Error" on the screen

# INT 01

- For single stepping the trap flag must be 1

- After execution of each instruction, 8086 automatically jumps to 00004H to fetch 4 bytes for CS: IP of the ISR.

- The job of ISR is to dump the registers on to the screen

# INT 02 (Non maskable Interrupt)

• When ever NMI pin of the 8086 is activated by a high signal (5v), the CPU Jumps to physical memory location 00008 to fetch CS:IP of the ISR associated with NMI.

# INT 03 (break point)

- A break point is used to examine the CPU and memory after the execution of a group of Instructions.

- It is one byte instruction whereas other instructions of the form "INT nn" are 2 byte instructions.

# INT 04 (Signed number overflow)

- There is an instruction associated with this INT 0 (interrupt on overflow).

- If INT 0 is placed after a signed number arithmetic as IMUL or ADD the CPU will activate INT 04 if 0F = 1.

- In case where 0F = 0, the INT 0 is not executed but is bypassed and acts as a NOP.

# **Performance of Hardware Interrupts**

- NMI : Non maskable interrupts TYPE 2 Interrupt

- INTR : Interrupt request Between 20H and FFH

# **Interrupt Priority Structure**

| Interrupt                 | Priority |

|---------------------------|----------|

| Divide Error, INT(n),INTO | Highest  |

| NMI                       |          |

| INTR                      |          |

| Single Step               | Lowest   |